## MICS実験第一J2課題

## 論理回路とVerilog-HDL

## 八巻隼人

(yamaki@uec.ac.jp)

西10号館-519

## この実験資料について

- ・ダウンロード用 URL

- http://www.hpc.is.uec.ac.jp/yamaki\_lab/teaching-jp.html

- ・資料と共にsampleファイルが置いてあります。授業で出てくるvファイルはここに入っているので参考にしてください。 (./~.sc というスクリプトを実行するとiverilogコンパイルから実行まで一気に行ってくれます)

- ・佐藤証先生の「J2課題解説スライド」がベース

- ・佐藤証先生のオリジナル→ <a href="http://satoh.cs.uec.ac.jp/ja">http://satoh.cs.uec.ac.jp/ja</a>

## 参考書

- 赤い本:

- Verilog-HDL の勉強用

- 青い本:

- ・ツールの使い方の勉強用

## J2課題の目的

・論理回路の特性/設計技術を習得する

## J2課題の実施方法

- ・今年は対面実施となります.

- ・実施内容や課題は本資料に載っています

- それとは別に、問題のヒントを以下のリンクに随時upします. http://www.hpc.is.uec.ac.jp/yamaki\_lab/teaching-jp.html

- わからないことがあったら対応するので私にメールください

- 八巻 (yamaki@uec.ac.jp)

## 実験の流れ

- ・実験初日(~p43) ガイダンス 簡単な組み合わせ回路の設計 問題1~3

- ・実験2日目(~p60) 順序回路の設計 問題4

- ・実験3日目(~p71) 加減算回路の設計 問題5~7

### レポート

#### 記載内容と採点基準

- この資料の問題1~7を全て行い、その内容に考察を加えレポートとする

- 問題1~7全て回答できていることが修了の条件

- 更に出来る人は問題8を解くと加点

- 例年, 問題7まで解けずに単位を落とす人が結構います. わからない部分は恐れず質問してください.

#### 提出方法

- レポートPDF ファイルを WebClass 上で提出.

- 受付期間内なら何度でも再提出可.

#### <u>受付期間</u>

- 授業終了から3週間後の23:00まで

- 前半組: 7/30(水) の 23:00まで

- 後半組: 8/11(月) の 23:00まで

## 目次

- ・本実験の内容とその意義(論理回路とハードウェア設計)

- ・verilogの使い方

- 簡単な組み合わせ回路(問題1~3)

- ・順序回路(問題4)

- 加減算回路(問題5~7)

# 本実験の内容とその意義 論理回路とハードウェア設計

## 論理回路とは

- ・デジタル回路の数学的モデル

- ・デジタル回路: 1と0のデジタル信号のみを用いて様々な計算をする回路 (一般的には電圧のHighとLowを1と0にデジタル化)

・アナログ回路:連続するアナログ信号を用いて様々な計算をする回路

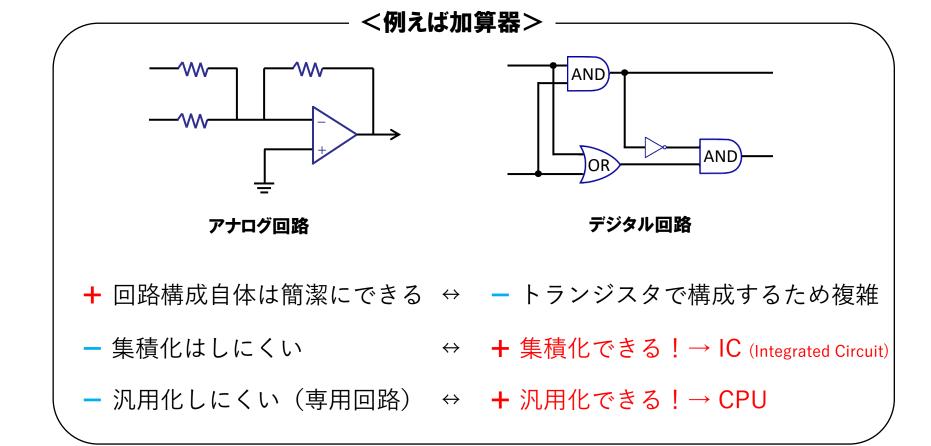

## デジタル回路の利点

・ある機能を実現したい場合,アナログ/デジタル回路どちらでも可だが

## ハードウェア?ソフトウェア?

• 文脈によりそれぞれが指す意味は多少異なる

#### 一般的には

- ハードウェア:物理的実体を持つ機械部品.

例. CPU, メモリ, マウス, キーボード, ディスプレイ

- ソフトウェア:物理的実体を持たない構成要素. 主にプログラムのこと.

例. OS, アプリケーションプログラム, ドライバ

#### 処理において使われる時(ハードウェア処理、ソフトウェア処理)

- ハードウェア:専用の論理回路による処理

- ソフトウェア: CPUによる (プログラムでの) 処理

#### 本実験の文脈はこちら

## ハードウェアとソフトウェア 何が違う?

#### ~ソフトウェア(CPU)の場合~

#### 例えば…

- 次のような計算をCPUで実行する場合  $x = (a \times 10 + 20) + (b \times 100 50)$

- CPUでは以下のように実行に 5 命令(5 サイクル)を要する

乗算命令 → 加算命令 → 乗算命令 → 減算命令 → 加算命令

## ハードウェアとソフトウェア 何が違う?

#### ~ハードウェアの場合~

• その処理専用の回路(ASIC)を作れば高速に処理できる

#### 例えば…

先ほどの例↓

$$x = (a \times 10 + 20) + (b \times 100 - 50)$$

• ハードウェアでは 1 サイクル で計算が完了する

x = (a×10 + 20) + (b×100-50) を計算する回路 (この回路は適当…)

#### Tips

ソート処理を考えてみるとより差がわかりやすい.

ソート処理はCPUの場合, 値の大小で入れ替えを繰り 返すので結構なサイクルを 要する

一方でハードウェアの場合, ソート回路に値を入れると 1サイクルで結果が得られる 超高速

## ハードウェアとソフトウェア 何が違う?

#### ~まとめると~

- ハードウェア処理は超高速

- また, (あまりにも複雑な処理でなければ) CPUやメモリを実装するより 専用論理回路を実装したほうが小規模

#### 小型とか超高速を重視する処理において有用

#### 例えば…

- ・動画像処理

- ・組み込み機器系(監視カメラ、loTセンサとか)の処理

- ・ルータのパケット処理

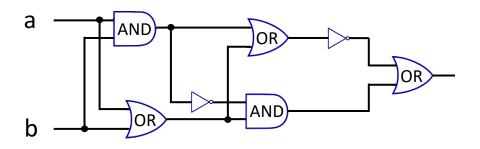

## ハードウェア設計(この実験)

- ハードウェア(専用論理回路)はどうやって作る?

- ① まず仕様を満たす論理回路の設計図を作成する

- 仕様から状態遷移図・真理値表を描き,入出力の論理式を求める

- 導いた論理式をもとに回路図を作成

#### 論理回路設計の講義でやった

- ② テストベンチを用いて設計した回路の動作を検証

- 回路作成には膨大なお金がかかるので失敗はできない

- シミュレーションにより回路が所望の動作をするか徹底的に検証

ハードウェア記述言語 verilog

③ 論理回路(実物)を作成 膨大なお金をかけて外注する

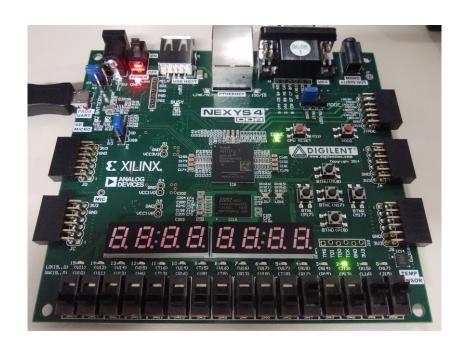

## ハードウェア設計の③について

- 実物の回路を作ってもらうにはとにかくお金がかかる(数百万円~)

- そこで最近は FPGA (Field Programmable Gate Array) が出てきた

- FPGAは…

- 論理回路を(外注せずとも) 自作できるハードウェア

- FPGAのお値段は数万円~

- 回路を作る費用はタダ

- しかも設計した論理回路を 自分でPC上で焼ける

- 何度でも焼き直し可能という 夢のようなデバイス

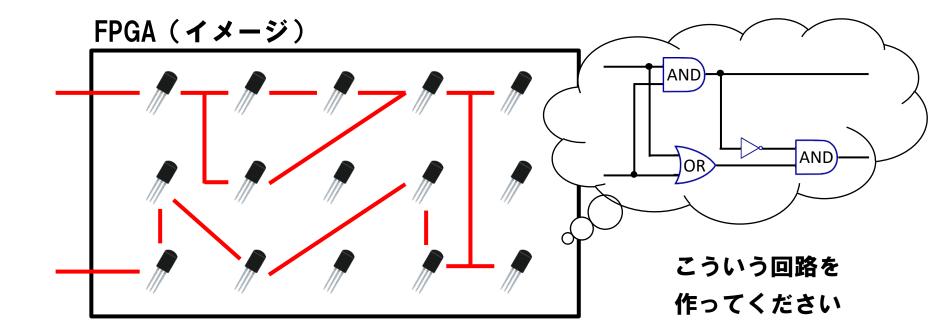

## FPGA (のイメージ)

#### Field Programmable Gate Array

- ゲート(トランジスタ)がアレイ(格子)状に配置されている

- Verilog で作成した回路となるようにFPGAのゲートを配線

- → 所望の論理回路を作成できる(配線しなおすことも可能)

## ハードウェア記述言語 verilog

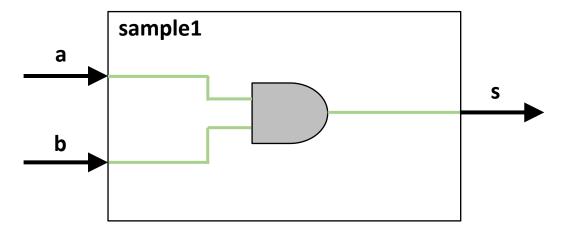

## Verilog-HDL の例: AND回路のモジュール (sample 1.v)

・まずは以下のverilogプログラムを自分で作ってみましょう コマンドラインで \$ vi sample1.v または \$ emacs sample1.vとし 以下を作成

```

module sample1(s, a, b); /* モジュール名(入出力端子)

input a, b; /* 入力端子a, bの宣言

output s; /* 出力端子sの宣言

assign s = a & b; /* s に a (and) b を接続

endmodule

```

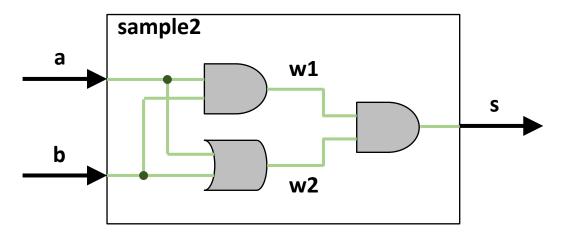

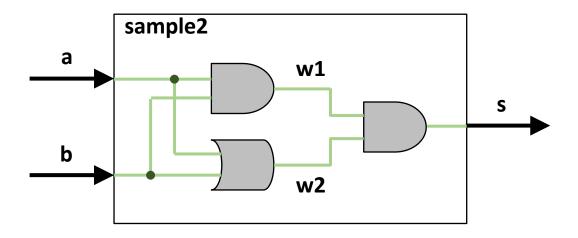

## Verilog-HDL の例: wireの使い方 (sample2.v)

- モジュール内で必要になる配線はwireで宣言

- assign文は出力や配線に接続するための構文(後述するregはassignを使わない)

```

module sample2(s, a, b); /* モジュール名(入出力端子)

input a, b; /* 入力端子a, bの宣言

output s; /* 出力端子sの宣言

wire w1, w2; /* 配線w1, w2の宣言

assign w1 = a & b; /* w1 に a (and) b を接続

assign w2 = a | b; /* w2 に a (or) b を接続

endmodule

endmodule

```

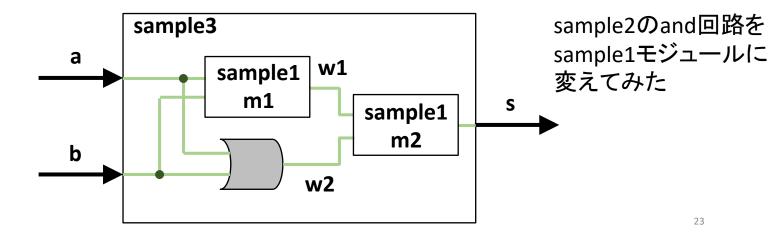

## Verilog-HDL の例:モジュールの入れ子 (sample3.v)

モジュール内で別モジュールを呼び出すことも可能

```

module sample3(s, a, b); /* モジュール名(入出力端子)

input a, b; /* 入力端子a, bの宣言

output s; /* 出力端子sの宣言

wire w1, w2; /* 配線w1, w2の宣言

sample1 m1(w1, a, b); /* sample1モジュールを呼び出し

sample1 m2(s, w1, w2); 引数の順番はsample1・vと対応

assign w2 = a | b; /* w2 に a (or) b を接続

endmodule

```

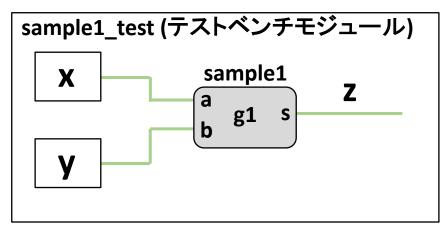

## モジュールの実装→動作確認 (テストベンチ)

- ・以上で簡単な回路ならもう記述できるようになりました

- モジュールが完成したら、その動作確認が必要

- ・以下の回路なら, aとbにテスト信号を流し, 正しいsが得られるか確認 a, bが(0,0), (0,1), (1,0), (1,1) の時, sが 0, 0, 0, 1 になるかどうか

- ・作ったモジュールに手を加えて動作確認するのはよろしくない そこで動作確認用のテストベンチモジュールを作る

## Verilog-HDL の例: sample1のテストベンチ (sample1\_test.v)

```

テストベンチの場合、

入出力端子は作らない。

入力側をregで

(詳しくは後述)

出力側をwireで宣言。

間違えやすいので注意

```

モニタで指定した信号に (今回ならx,y,z,stime) 変化があった場合に ディスプレイ出力

> C言語でいう Printf

```

module

sample1 test;

wire

z;

reg

x, y;

sample1 g1(z, x, y);

initial

/* イベントの生成

begin

$monitor(" %b %b %b", x, y, z, $stime);

$display(" x y z

time");

x=0; y=0; /* 0サイクル目

/* 50サイクル目

#50 v=1;

#50 x=1; y=0; /* 100サイクル目

/* 150サイクル目

#50 y=1;

#50 $finish:

/* 200サイクル目

end

endmodule

```

テストイベント 今回は50サイクル毎に 入力値を変化

## iverilogを使った動作確認

・コンパイル

iverilog -o 実行ファイル名 -s トップモジュール名 コンパイルしたい.vファイル群

```

[ @blue99 sample]$ iverilog -o sample1 -s sample1_test sample1_test.v sample1.v

```

- → エラーが出なければsample1というファイルが作成される

- ・シミュレーションの実行

vvp 実行ファイル名 または 実行ファイルを直接指定 ./sample1

| [ |   |   | @blue99 | sample]\$ vvp sample1 |

|---|---|---|---------|-----------------------|

| а | b | S | time    | \$displayの内容          |

| 0 | 0 | 0 | 0       |                       |

| 0 | 1 | 0 | 50      | <b>☆</b>              |

| 1 | 0 | 0 | 100     | \$monitorの内容          |

| 1 | 1 | 1 | 150     | _                     |

→ 自分が意図した通りの結果となっているか確認

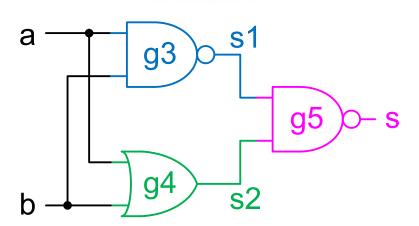

## 一致検出回路(eq.v)

```

module eq(s, a, b); /* 一致検出回路 */

input a, b;

output s;

wire na, nb, s1, s2;

assign na = ~a, nb = ~b;

assign s1 = a & b, s2 = na & nb;

assign s = s1 | s2;

endmodule

```

#### 各記号の意味

- ~: NOT演算

- &: AND演算

- |: OR演算

| 真        | 理値  | 表    | 回路図                                           |  |  |

|----------|-----|------|-----------------------------------------------|--|--|

| а        | b   | S    | $a \xrightarrow{g3} s1$                       |  |  |

| 0        | 0   | 1    |                                               |  |  |

| 0        | 1   | 0    | $\frac{1}{g1}$ $\frac{na}{g5}$ $\frac{g5}{s}$ |  |  |

| 1        | 0   | 0    | g4                                            |  |  |

| 1        | 1   | 1    | b q2 s2                                       |  |  |

| 入力a, bがー | 致した | 時に出力 | วรทั่ 1                                       |  |  |

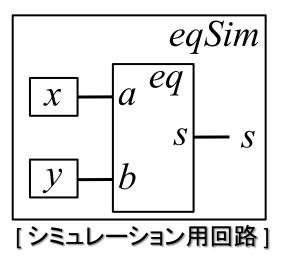

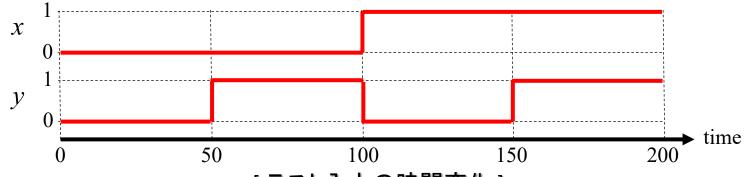

## ·致検出回路のテストベンチ(eqSim.v)

```

/* 一致検出回路の */

/* シミュレーション */

eqSim;

module

wire s;

reg

х, у;

g1(s, x, y);

initial

← 制御記述

begin

$monitor(" %b %b %b", x, y, s, $stime);

$display(" x y s

time");

x=0; y=0;

#50

y=1;

#50

x=1; y=0;

┡ヲスト入力

y=1;

#50

#50

$finish;

end •

遅延

endmodule

```

[テスト入力の時間変化]

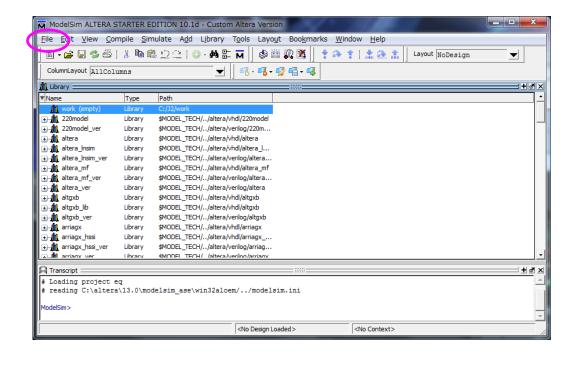

## ModelSimの使い方

すみません, 今年度はCEDの環境変更に伴いModelSimが使えません

代わりに gtkwave というツールを使います 使い方は Webclass の実験ページに書いてありますので そちらを参照してください

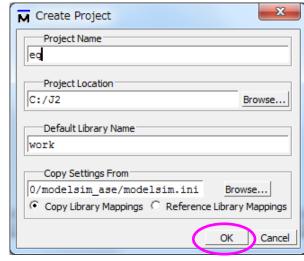

## ModelSimの起動とプロジェクト作成

- 1. コンソールで"mkdir ~/mics\_J2"と入力

- 2. コンソールで"vsim"(今年は"vsim2"?)と入力

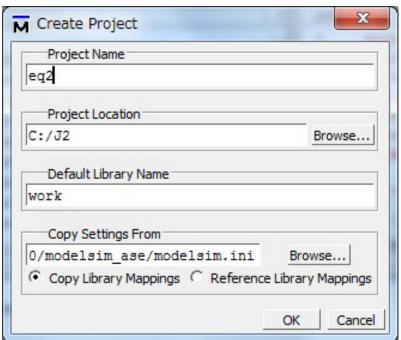

- 3. File→New→Proeject... で"Create Project"ウィンドウが開く

- 4. Project Name: eq

- 5. Project Location: /path\_to\_homedir/mics\_J2

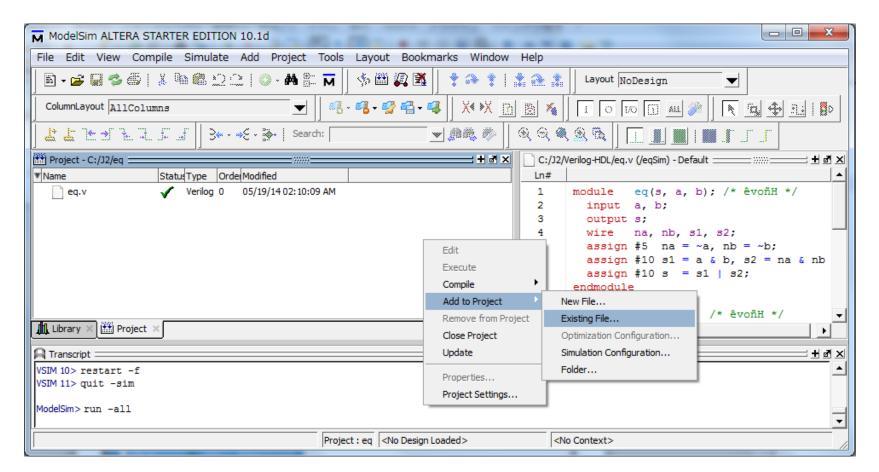

## Verilog-HDLファイルの追加

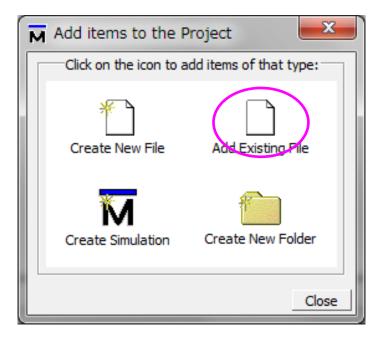

- 1. "Add items to the Project"ウィンドウ: Add Existing File またはメインウィンドウから Project→Add to Project→Existing File…

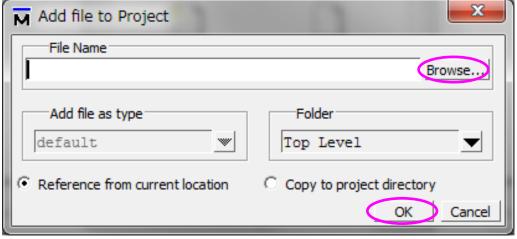

- 2. "Add file to Project"ウィンドウ: Browse

- 3. "Select files to add to project"ウィンドウ:

- 4. eq.vと eqSim.v を選択して開く.

- 5. "Add file to Project"ウィンドウ: OK

- 6. "Add items to the Project"ウィンドウ: Close

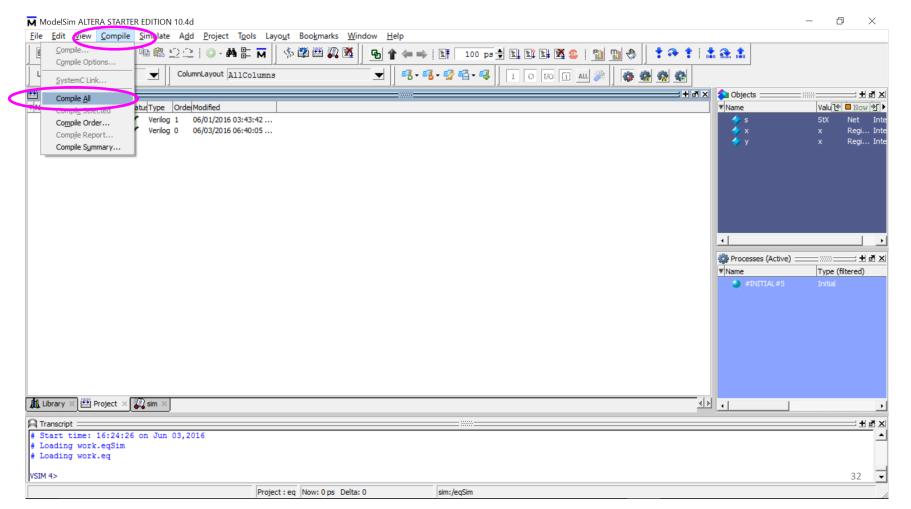

### コンパイル

- ・メインウィンドウ: Compile→Compile All

- Verilog-HDLファイルのStatusが?からレに変わり、"Compile of eqSim.v was successful." "Compile of eq.v was successful" と出る.

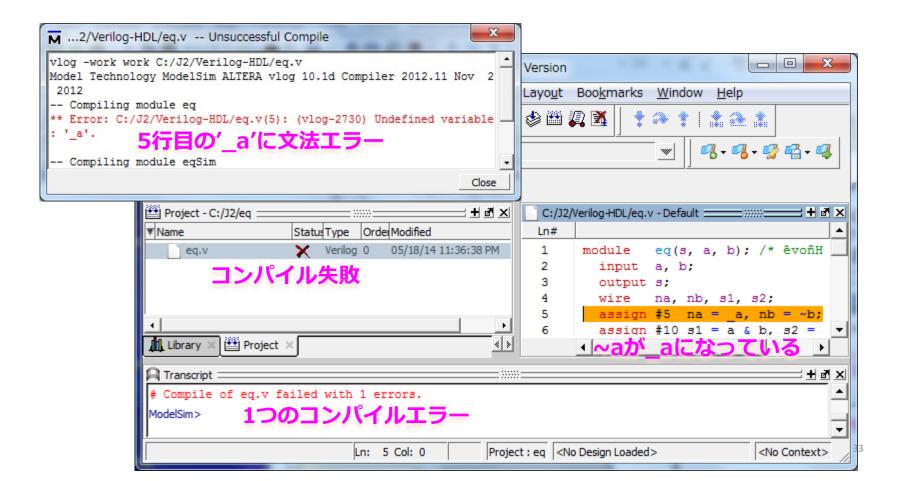

### コンパイルエラー

- エラーがあるとTranscriptウィンドウに赤く表示されるので、そこをダブルクリックするとエラーの詳細が表示される

- ・さらに"\*\* Error: "の赤い行をクリックするとソースコードウィンドウが開いてエラーの行がオレンジで表示される

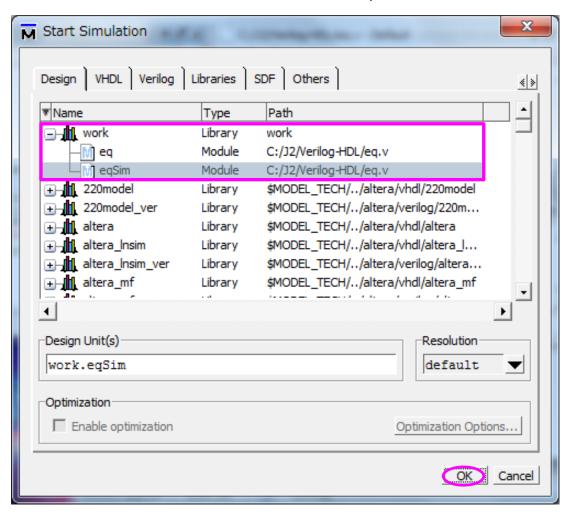

## シミュレータ起動

- Simulate→Start Simulation

- Start Simulationウィンドウでwork/eqSimを選択

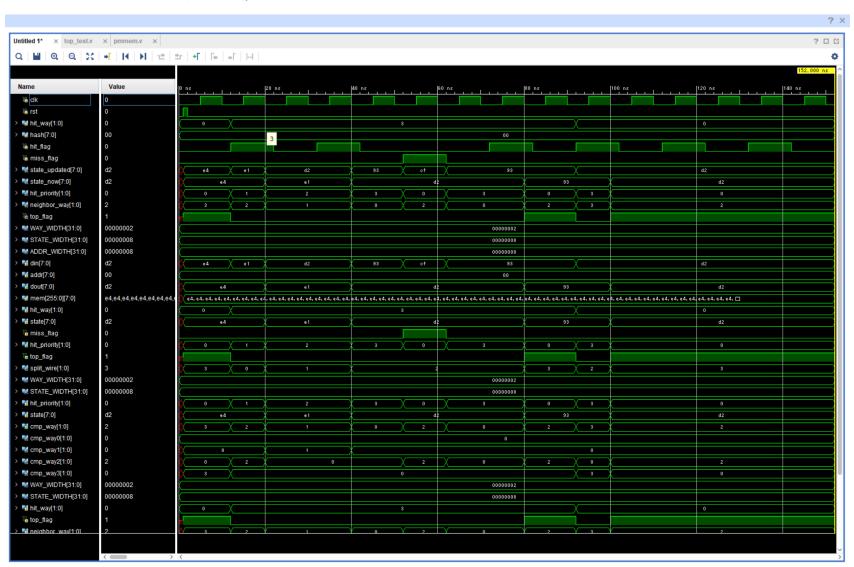

## シミュレーション設定

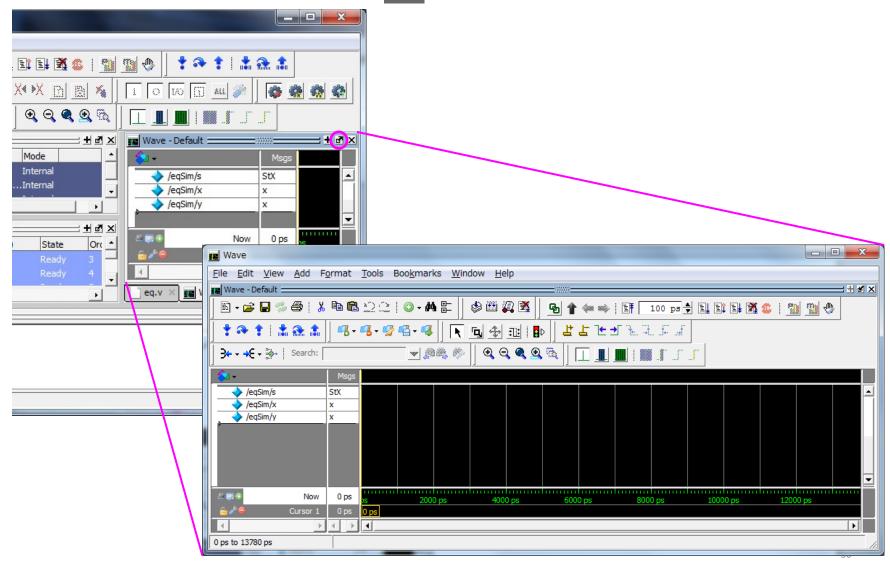

- シミュレーションウィンドウが開く

- ・Add→add to wave→all items in regionで波形ウィンドウが開く

- ・"All items in region and below"と"All items in design"は下位レベルやソースの全ての信号線が表示される

## シミュレーション設定

・ウィンドウが小さいので 🕝 ボタンを押して拡大

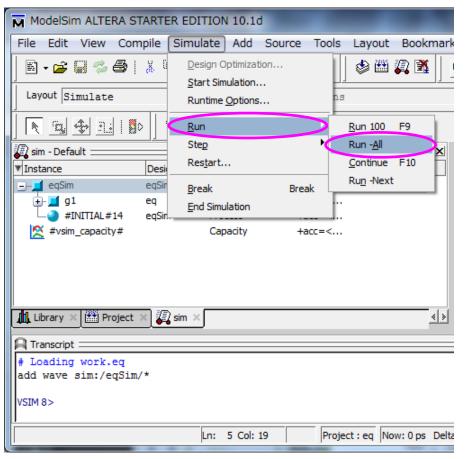

## シミュレーション実行

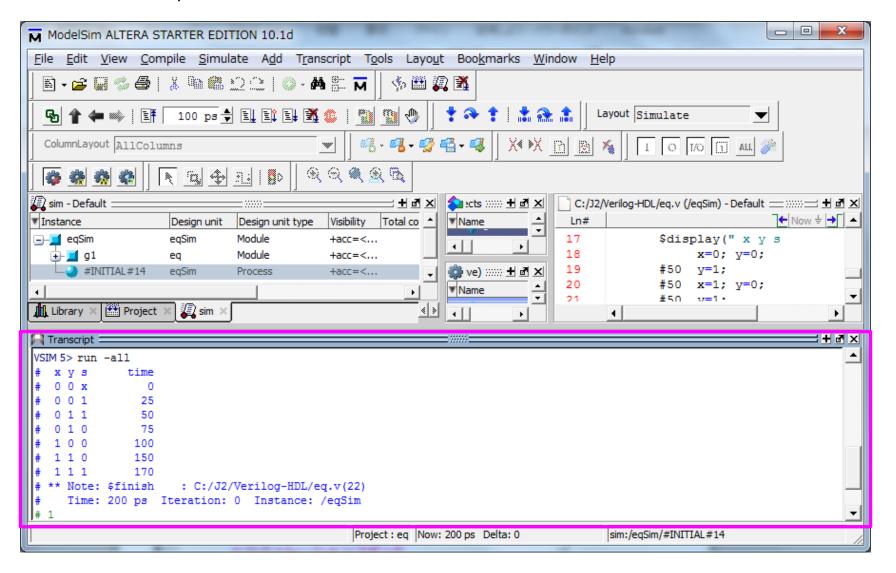

- ・メインウィンドウで、Simulate→Run→All

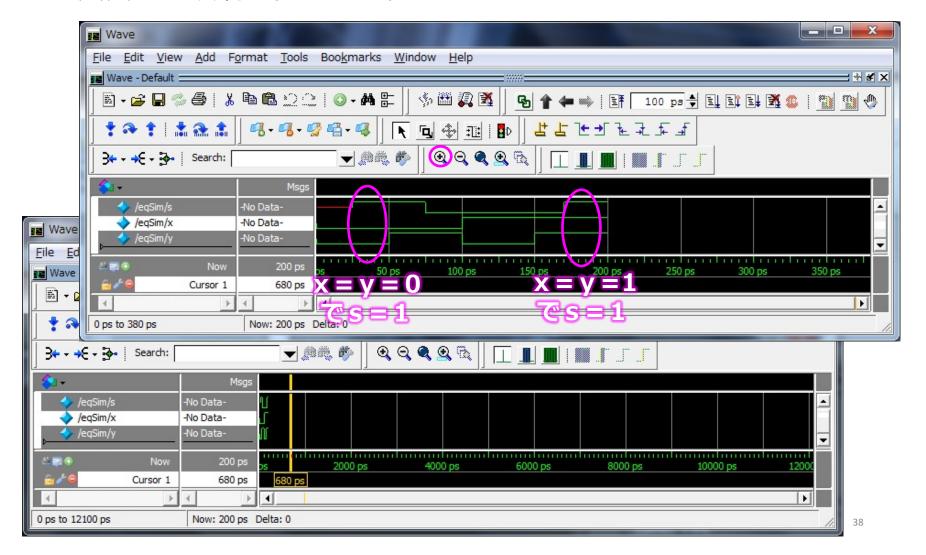

- Finsh Vsimウィンドウで「いいえ(N)」を選択

- 「はい(Y)」を選択するとModelSimが終了してしまうので注意

### シミュレーション結果表示

- ・Waveウィンドウに結果が表示される

- ・画面を虫眼鏡で拡大して表示

### シミュレーション結果表示

シミュレーションモジュールに\$monitorコマンドを記述しているのでTranscriptウィンドウにテキストでも表示される

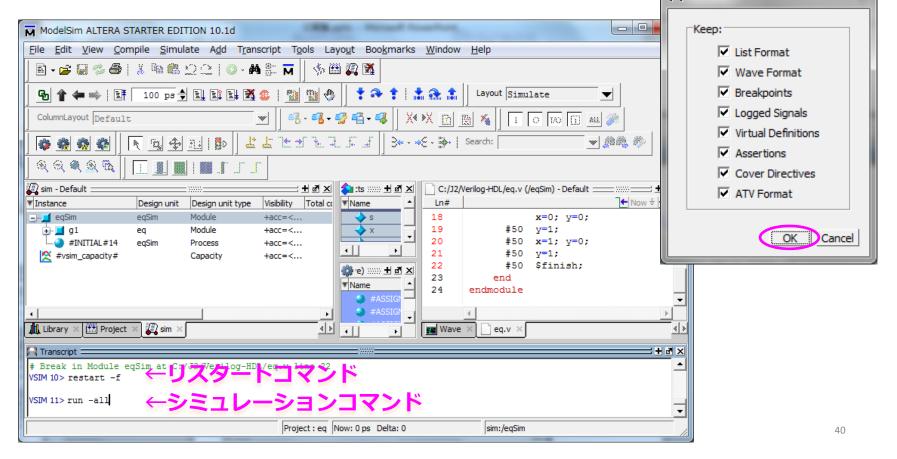

#### 再シミュレーション

- ・メインウィンドウで Simulate→Restart

- Restartウィンドウが出るのでOKをクリック

- ・「シミュレーションの実行」に戻って再シミュレーション

全てのコマンドはTranscriptウィンドウで実行されているので、

M Restart

#### 内部信号の表示

- ・Simウィンドウでモジュールを指定し,内部信号を表示

- ・\$monitor関数では "g1.s1"のようにモジュール内の信号やさらに"."でつ ないでモジュール内のモジュールを指定

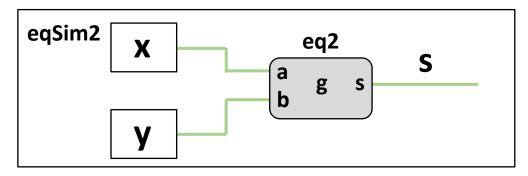

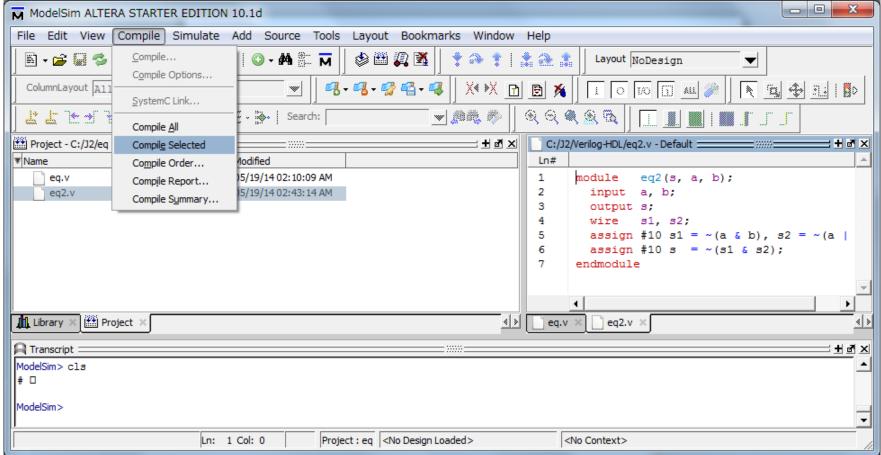

- Simulate→End Simulation

- Projectウィンドウで右クリックしてポップアップメニューを出し, Add to Project→Existing File...

- eq2.v と eqSim2.v を追加

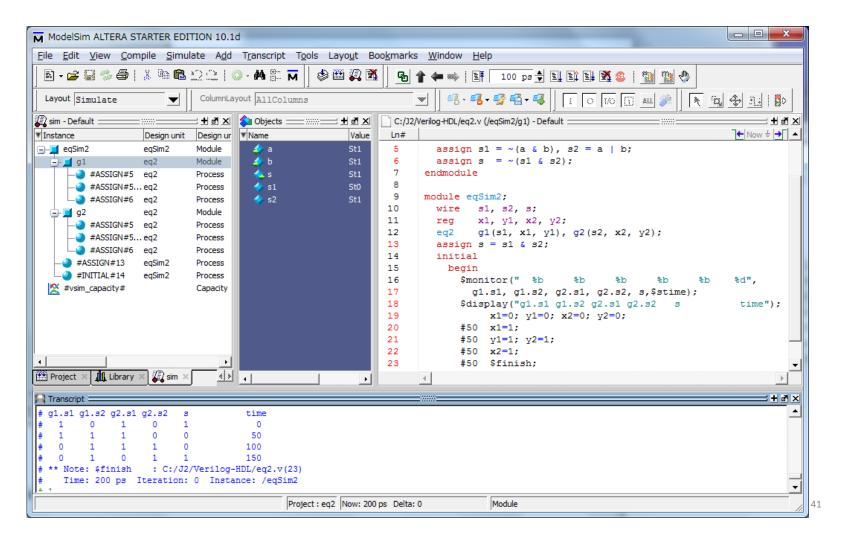

```

module eq2(s, a, b);

input a, b;

output s;

wire s1, s2;

assign s1 = ~(a & b), s2 = a | b;

assign s = ~(s1 & s2);

endmodule

```

#### 真理値表

| Α | В | A=B |

|---|---|-----|

| 0 | 0 |     |

| 0 | 1 |     |

| 1 | 0 |     |

| 1 |   |     |

#### 回路図

```

module eqSim2;

wire s;

reg x, y;

eq2 g(s, x, y);

initial

begin

$monitor( " %b %b", g.s1, g.s2, $stime);

$display("g. s1 g. s2 time");

x=0; y=0;

#50 x=1;

#50 y=1;

#50 x=0;

#50 $finish;

end

endmodule

```

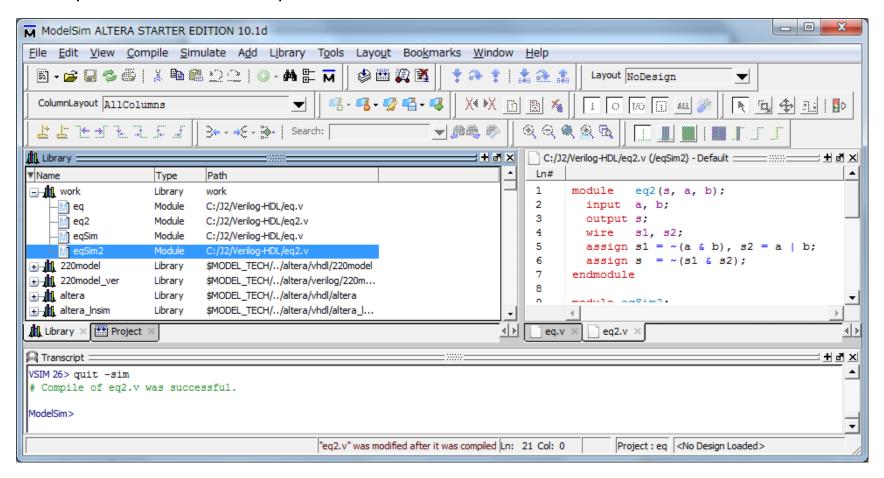

・Window内の追加したファイルを選択して, Compile→Compile Selected(選択したファイルが対象)または Compile All(すべてのファイルが対象)でコンパイル

- ・Libraryタグのworkの下に, eq2とeqSim2ができている

- •eqSimと同様にeqSim2をシミュレーション

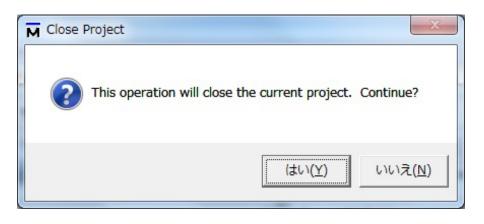

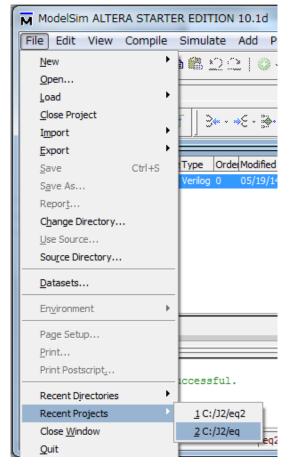

### プロジェクトの変更

- File→Close Projectでプロジェクトを閉じる

- File→New Projectで新しいプロジェクトを作る

- 前のプロジェクトを閉じていない時は閉じるかどうか聞かれる

- Project Name: eq2で新しいプロジェクトを開く

- ・他のプロジェクトとモジュールを共有するときや、名前が同じ異なるモジュールがなければDefault Library Name: workでよい

#### プロジェクトの変更

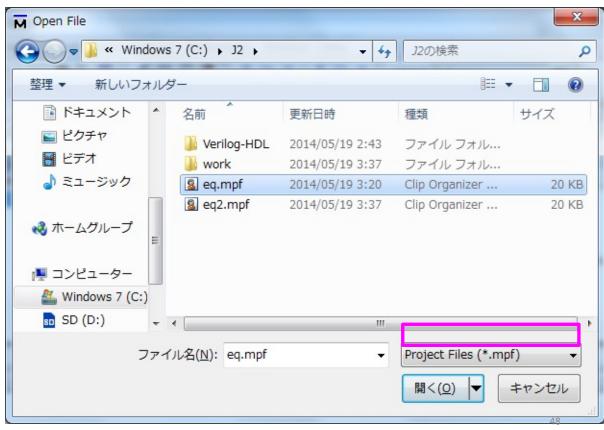

・プロジェクトeqに戻るときはFile→Resent Projectから選ぶか, File→Openでファイル選択のポップアップウィンドウの右下 を"Project Files"に切り替えてmpf (Modelsim Project File) ファイルを表示して選択

# 簡單念組み合わ世回路

- ・モジュール eq の動作検証を eqSim を用いて行い,出力結果が正しくなるかどうか確認せよ.なお,検証には\$monitorを用い,x,y,sをCUI上に表示して確認すること.

- また、eqSimを改良し、eqモジュールの内部信号であるs1、s2を\$monitorでCUI上に表示できるようにせよ。

\$monitor文において、入れ子となっているモジュールの内部信号を観測するには "モジュール名.信号名"を使う。例として、p.35のeqSim2の\$monitor文、\$display文を参考にせよ。

・入力信号 a, b, c, d を受け取り, $a = b \ b \ c = d$  がともに成り立つとき出力信号 s を 1 に,それ以外のときs を 0 にする回路のモジュールを,モジュールeq を 2 個使って作れ.

・問題2で設計したモジュールの動作検証を行うテストベンチを作成せよ.また、作成したテストベンチモジュールを用いて、動作検証せよ.動作検証は、ModelSimを用いて、入出力信号の波形をGUI表示して確認すること.

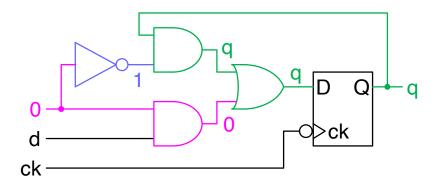

### 組み合わせ回路と順序回路

・組み合わせ回路:現在の入力のみによって出力が一意に決まる ここまで作成してきた回路は全て組み合わせ回路

・順序回路:過去の入力により出力が変化する

→ すなわちデータを記憶している

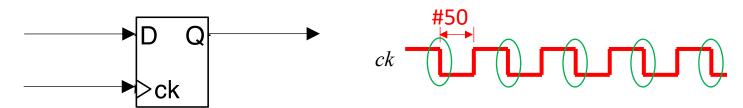

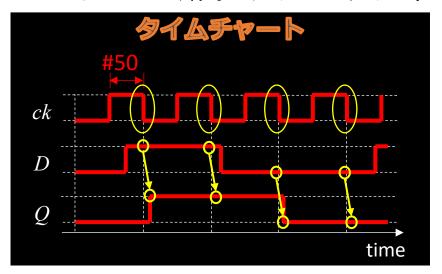

#### Dフリップフロップ

最も単純な順序回路

クロック信号に同期して出力を生成

従って次の周期に達するまでは入力が変化しても出力は不変

= 前周期の入力が次周期まで記憶される

## Verilogでの順序回路作成

- ・レジスタ(reg)とalways文を使うことで、順序回路を作成できる

- レジスタ…値を保存できる極小のメモリ

wireが配線だったのに対し、レジスタ(regとして宣言)は

データを格納する箱のイメージ

- ・always文…always @(イベント) 処理内容

"イベントが起こる時,毎回 *処理内容* を実行する"という構文

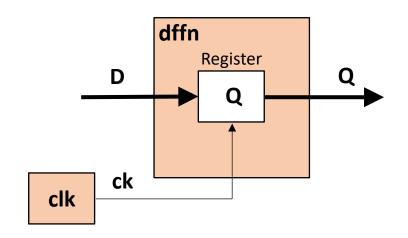

# Dフリップフロップ(Delay Frip Frop)

クロック信号生成モジュール clk

Reg の値を output したい時 同じ名前で定義 してもよい

```

module   clk(ck);

output   ck;

reg    ck;

initial ck = 0;

always #50 ck = ~ck;

endmodule

```

50サイクル経過する度に ck の値を反転

Ckが下がった瞬間の入力Dが出力Q

Dフリップフロップ dffn

```

module dffn(Q, D, ck);

input D, ck;

output Q; レジスタの初期化

reg Q;

initial Q = 0;

always @(negedge ck) Q = D;

endmodule

```

Ckが下がる度にその時のDをQ1に保存

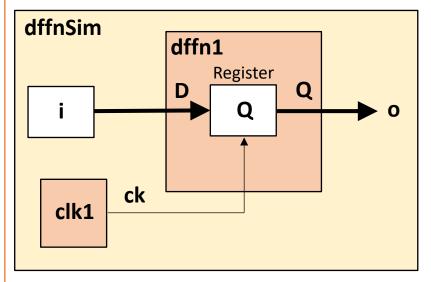

#### Dフリップフロップのテストベンチ

```

module

dffnSim;

i;

reg

wire o;

clk clk1(ck);

dffn dffn1(o, i, ck);

initial

begin

$monitor(" %b %b %b",

ck,i,o,$stime);

$display("ck i o time");

i = 0;

#100 i = 1;

#200 i = 0;

#100 $finish;

end

endmodule

```

#### もう少し複雑な順序回路:1ビットの記憶回路

・制御信号 I でD-FFへの書き込みを制御

```

module r1(q, l, d, ck);

input l, d, ck;

output q;

wire nl, s1, s2, d1;

dffn f(q, d1, ck);

assign nl = ~l;

assign s1 = nl & q, s2 = l & d;

assign d1 = s1 | s2;

endmodule

```

#### I = 0 のとき q を保持

#### l = 1 のとき d を書込み

#### 仕様からverilogで回路を作成するには?

- ・前頁のように回路図が与えられれば、もうverilogで書けるはず

- それでは与えられた仕様から回路図を作るには?(論理回路の講義の復習)

- 1. まず仕様から状態遷移図・真理値表を作成

- 2. 出力と次遷移状態を,入力と現遷移状態の論理式で表す (真理値表からカルノー図を用いて求める)

- 3. 得られた論理式から回路図を作成

- 4. 回路図をverilogで書き直す

- ・次ページでは例として、**"スイッチaが押された状態でclkが立ち下がると、3クロックの間、1を出力する回路"**をverilogで作成する

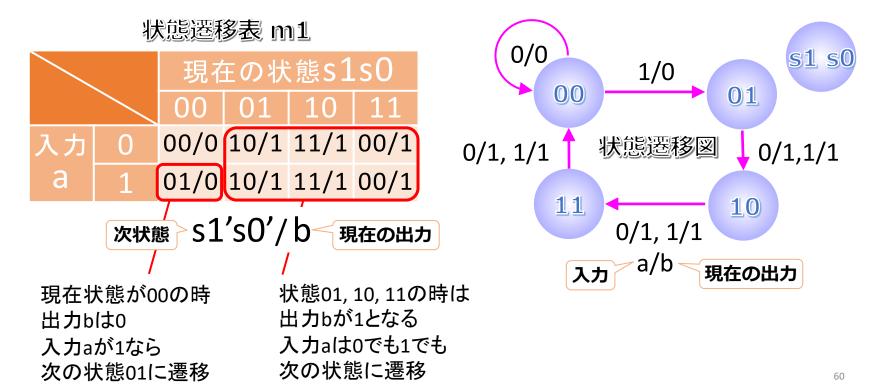

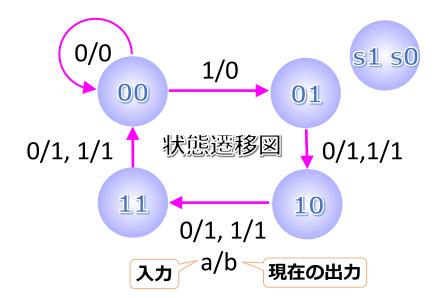

### 逐次制御回路1(仕様→状態遷移表・遷移図)

- 仕様:

- スイッチaが押された状態でclkが立ち下がると、3クロックの間、1を出力

- パラメータ:

- 入力a

- 出力b

- 現在の状態s1s0

- 次の状態s1's0'

### 逐次制御回路1(状態遷移図→真理値表)

・得られた状態遷移表、状態遷移図を基に真理値表を描く

#### 状態遷移表 m1

#### 真理值表

| a    | s1 | s0 | b | <b>s1</b> ′ | s0' |

|------|----|----|---|-------------|-----|

| 0    | 0  | 0  |   | 0           | 0   |

| 1    | 0  | 0  |   | 0           | 1   |

| X    | 0  | 1  | 1 | 1           | 0   |

| Х    | 1  | 0  | 1 | 1           | 1   |

| Х    | 1  | 1  | 1 | 0           | 0   |

| abla |    |    |   |             |     |

x はdon't careと言って, 0でも1でもどちらでも良いという意味

don't care でまとめるのが難しいなら a=0, a=1の2行に分けて描いても良い

### 逐次制御回路1(真理值表→論理式化)

- ・b, s1', s0' それぞれに関して**カルノー図**を作成し論理式化

- ・状態s1s0の00 01 11 10という順番に注意

- カルノー図でまとめられる単位は1,2,4…なので1×1や1×2,2×2でまとめる

カルノー図(b)

|    |   | がある一国 (B)<br>状態s1s0 |   |   |   |

|----|---|---------------------|---|---|---|

|    |   | 00 01 11 10         |   |   |   |

| 入力 | 0 | 0                   | 1 | 1 | 1 |

| а  | 1 | 0                   | 1 | 1 | 1 |

カルノー図 (s1')

|    |   | 状態s1s0 |    |    |    |  |  |

|----|---|--------|----|----|----|--|--|

|    |   | 00     | 01 | 11 | 10 |  |  |

| 入力 | 0 | 0      | 1  | 0  | 1  |  |  |

| а  | 1 | 0      | 1  | 0  | 1  |  |  |

カルノー図(s0')

|    |   | 状態s1s0      |   |   |     |  |

|----|---|-------------|---|---|-----|--|

|    |   | 00 01 11 10 |   |   |     |  |

| 入力 | 0 | 0           | 0 | 0 | 1   |  |

| а  | 1 | 1           | 0 | 0 | 1 - |  |

真理值表

| а | s1 | s0 | b | <b>s1</b> ′ | s0' |

|---|----|----|---|-------------|-----|

| 0 | 0  | 0  |   | 0           | 0   |

| 1 | 0  | 0  |   | 0           | 1   |

| Х | 0  | 1  | 1 | 1           | 0   |

| Χ | 1  | 0  | 1 | 1           | 1   |

| Х | 1  | 1  | 1 | 0           | 0   |

$$b = s0 + s1$$

$$s1' = \overline{s1 \cdot s0} + s1 \cdot \overline{s0}$$

$$s0' = a \cdot s0 + s1 \cdot s0$$

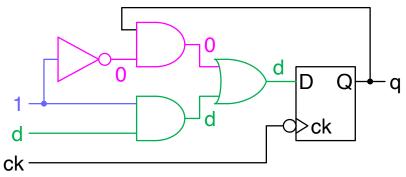

# 逐次制御回路1 (論理式→回路図・実装)

$$s1' = \overline{s1 \cdot s0} + \overline{s1 \cdot s0}$$

$s0' = \overline{a \cdot s0} + \overline{s1 \cdot s0}$

$b = s1 + s0$

今回は状態s1s0で 2bit分のFFが必要

ns1

ns0

2個のFFを中心に b, s1', s0'を信号で 接続する

a

ck

```

module m1(b, a, ck);

input a, ck;

output b;

wire ns1, ns0, s1, s0, d1, d0, c1, c2, c3;

dffn f1( s1, d1, ck ), f2( s0, d0, ck );

assign ns1 = ^s1, ns0 = ^s0;

assign c1 = s1 \& ns0, c2 = ns1 \& s0,

c3 = a \& ns0;

assign d1 = c1 | c2, d0 = c1 | c3,

b = s1 | s0;

endmodule

図が描けたら

verilogで

書き直すだけ

c2

d1 s1'

s1

c1

>ck

d0|s0′

сЗ

s0

63

```

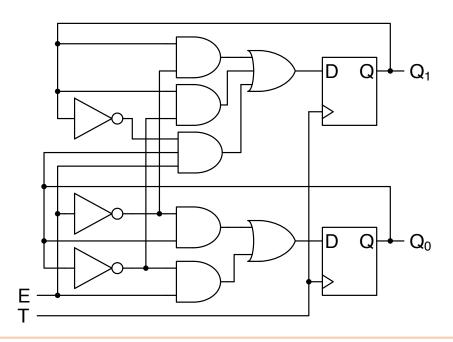

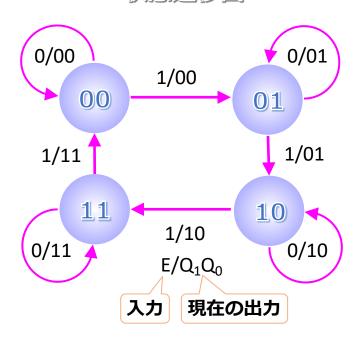

# 逐次制御回路2(回路図→状態遷移表→仕様)

- ・順序回路を状態遷移図で表記して動作を解析,あるいは状態 遷移図から順序回路を設計するときにはFFの値が「状態」を 表す

- 入力と出力によってその状態間がどう遷移するかを調べる

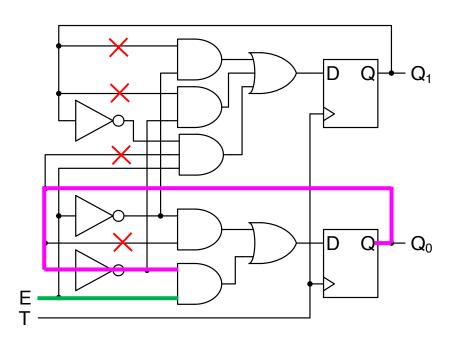

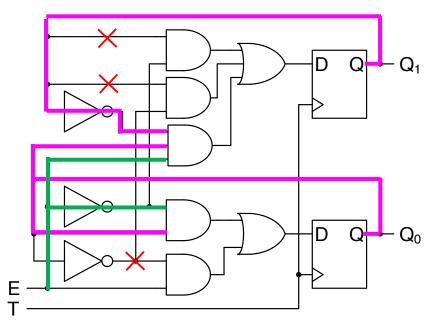

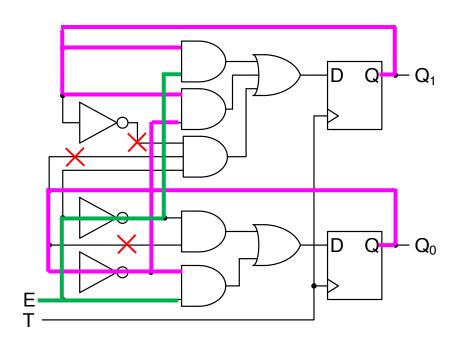

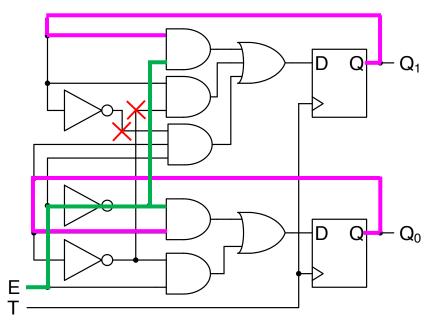

- CS実験第一J1課題の回路の動作を調べる

- 入力はE, 出力はQ<sub>1</sub>Q<sub>0</sub>

- 状態は $Q_1Q_0$  (D-FFから直接なので出力と一致)

- 2bitなので最大で4状態だが、全ての組合せを取らない場合もある

### 逐次制御回路2(状態遷移の確認)

#### <u>状態Q<sub>1</sub>Q<sub>0</sub>=00の場合</u>

- ・E=1の時、 $Q'_1=0$   $Q'_0=1$ となる ・E=1の時、 $Q'_1=1$   $Q'_0=0$ となる

#### <u>状態Q<sub>1</sub>Q<sub>0</sub>=01の場合</u>

- •E=0の時、 $Q'_1=0 Q'_0=0$ となる •E=0の時、 $Q'_1=0 Q'_0=1$ となる

### 逐次制御回路2(状態遷移の確認)

#### <u>状態Q<sub>1</sub>Q<sub>0</sub>=10の場合</u>

- ・E=1の時、 $Q'_1=1Q'_0=1$ となる ・E=1の時、 $Q'_1=0Q'_0=0$ となる

#### <u>状態Q<sub>1</sub>Q<sub>0</sub>=11の場合</u>

- ・E=0の時、 $Q'_1=1 Q'_0=0$ となる ・E=0の時、 $Q'_1=1 Q'_0=1$ となる

#### 逐次制御回路2(真理値表・状態遷移図)

#### <u>真理値表からE,Q1Q0とQ'1Q'0の関係を求める</u>

#### 状態遷移図の作成

| 直理    | 直表 |

|-------|----|

| 75/2E |    |

| Е | $Q_1$ | $Q_0$ | Q' 1 | Q'。 |

|---|-------|-------|------|-----|

| 0 | 0     | 0     | 0    | 0   |

| 0 | 0     | 1     | 0    | 1   |

| 0 | 1     | 0     | 1    | 0   |

| 0 | 1     | 1     | 1    | 1   |

| 1 | 0     | 0     | 0    | 1   |

| 1 | 0     | 1     | 1    | 0   |

| 1 | 1     | 0     | 1    | 1   |

| 1 | 1     | 1     | 0    | 0   |

#### 状態遷移図

1が入力されるたびに、カウントアップされた値(<4)を出力する回路 だとわかる

#### 逐次制御回路2(論理式の確認)

・カルノー図から $Q_1$ ,  $Q_0$  の式が求められる

カルノー図 (Q'1)

|    |   | 1  | 犬態( | Q1Q( | )  |

|----|---|----|-----|------|----|

|    |   | 00 | 01  | 11   | 10 |

| 入力 | 0 | 0  | 0   | 1    | 1  |

| Е  | 1 | 0  | 1   | 0    | 1  |

カルノー図 (Q'0)

|    |   | 7  | 犬態( | 21Q( |    |

|----|---|----|-----|------|----|

| Ì  |   | 00 | 01  | 11   | 10 |

| 入力 | 0 | 0  | 1   | 1    | 0  |

| Е  | 1 | 1  | 0   | 0    | 1  |

#### 真理值表

| Е | $Q_1$ | $Q_0$ | Q' <sub>1</sub> | Q' <sub>0</sub> |

|---|-------|-------|-----------------|-----------------|

| 0 | 0     | 0     | 0               | 0               |

| 0 | 0     | 1     | 0               | 1               |

| 0 | 1     | 0     | 1               | 0               |

| 0 | 1     | 1     | 1               | 1               |

| 1 | 0     | 0     | 0               | 1               |

| 1 | 0     | 1     | 1               | 0               |

| 1 | 1     | 0     | 1               | 1               |

| 1 | 1     | 1     | 0               | 0               |

$$Q'_{1} = E \cdot \overline{Q}_{1} \cdot Q_{0} + Q_{1} \cdot \overline{Q}_{0} + \overline{E} \cdot Q_{1}$$

$$Q'_0 = \overline{E} \cdot Q_0 + E \cdot \overline{Q}_0$$

→ 回路図と照らし合わせて一致しているかどうか

- ・以下の状態遷移表m2に従って動く回路m2の状態遷移図を書き, 回路を設計せよ.

- ・なお、回路m2は、初期状態 0 において入力 a に 1 が入力された状態でクロックが立ち下がると、状態 1 に遷移する. 以降、同様の操作が行われる度に状態 2 、3 と遷移し、最終的に出力 b から 1 を出力し、初期状態 0 に戻る.

- ・回路m2とそのテストベンチを実装し、シミュレーションで動作を確かめよ。ただし、回路m2の状態は、reg ではなく、2個のdffn を用いて実装すること。

- ・上記のシミュレーション結果の何をもって動作確認としたのかも 説明せよ.

#### 状態遷移表 m2

|    |   | 現在の状態S |     |     |     |

|----|---|--------|-----|-----|-----|

|    |   | 0      | 1   | 2   | 3   |

| 入力 | 0 | 0/0    | 1/0 | 2/0 | 3/0 |

| a  | 1 | 1/0    | 2/0 | 3/0 | 0/1 |

次状態 S / b 現在の出力

# 加減算回路

### 多ビットデータの表現

module eor4(z, x, y);

- ・多ビットのデータは, x[3:0]のように配列で表す (=x[3]x[2]x[1]x[0]の4bit値)

- Parameter 宣言を使うことでビット数を容易に変更できる

```

x[3:0] -

input [3: 0] x, y;

output [3: 0] z;

z[3:0]

wire [3:0] nx, ny, z1, z2; assign nx = x, ny = y;

assign z1 = x \& ny, z2 = nx \& y,

z = z1 \mid z2;

endmodule

module eorn( z, x, y );

x[n-1:0]

parameter n = 8;

y[n-1:0] n

input [n-1: 0] x, y;

output [n-1: 0] z;

wire [n-1: 0] nx, ny, z1, z2;

assign nx = x, ny = y;

eorn #4 e(g, a, b)

assign z1 = x \& ny, z2 = nx \& y,

と呼び出すことで

z = z1 \mid z2;

n=4に指定を変えることも可能

endmodule

```

#### ビットベクトル

- { }で信号を囲むことで複数の信号をまとめることが可能

- ・例えば, x[3:0]というのは{x[3:2], x[1:0]} {x[3], x[2], x[1], x[0]} と同じ

- ・ビットベクトルを使うとシフト操作等が実現できる

```

左シフト:{x[2:0], 1'b0} 左巡回シフト:{x[2:0], x[3]}

```

右シフト:{1'b0, x[3:1]} 右算術シフト:{x[3], x[3:1]}

※ 1'b0というのは1桁のb(2進数)の0という意味

例えば2進数の11も2'b11と書かないと10進数の11扱いされてしまう

```

module lshift( y, x );

input [3:0] x;

output [3:0] y;

assign y = {x[2:0], 1' b0};

endmodule

```

左1bitシフトのモジュール例

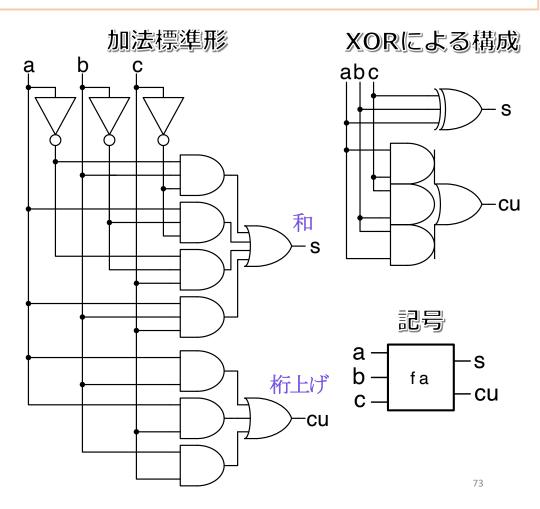

## 問題5の前提知識1 (加算回路の設計)

桁上げ cu = a & b | b & c | c & a

和 s = a & ~b & ~c | ~a & b & ~c | ~a & ~b & c | a & b & c

= a ^ b ^ c

全加算器(Full Adder) は下からの桁上げを考 慮した3入力の加算器

| а | b | С | cu | S |

|---|---|---|----|---|

| 0 | 0 | 0 | 0  | 0 |

| 0 | 0 | 1 | 0  | 1 |

| 0 | 1 | 0 | 0  | 1 |

| 0 | 1 | 1 | 1  | 0 |

| 1 | 0 | 0 | 0  | 1 |

| 1 | 0 | 1 | 1  | 0 |

| 1 | 1 | 0 | 1  | 0 |

| 1 | 1 | 1 | 1  | 1 |

$cu=a\cdot b+a\cdot c+b\cdot c$   $s=a\cdot \overline{b}\cdot \overline{c}+\overline{a}\cdot b\cdot \overline{c}$  $+\overline{a}\cdot \overline{b}\cdot c+a\cdot b\cdot c$

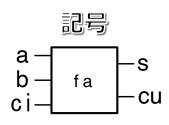

#### 問題5の前提知識2 (加算回路の設計)

・1ビット全加算器の場合(前頁を参考に)

```

module fa(cu, s, a, b, ci);

input a, b, ci;

output cu, s;

assign s = a ^ b ^ ci;

assign cu = a & b | b & ci | a & ci;

endmodule

```

```

0

・4ビット加算器を作るには?

cu

cu s

cu s

cu s

cu s

module\ add4(cu, s, x, y, ci);

fa

fa

fa

fa

[3: 0] x, y;

input

a b c

a b c

a b c

a b c

input

output

cu;

x_3 y_3 c_3

X_2 Y_2 C_2

X_1 Y_1 C_1

x_0 y_0 c_i

output [3: 0] s;

0 0

wire [3: 0] c;

a3(cu, s[3], x[3], y[3], c[3]),

fa

a2(c[3], s[2], x[2], y[2], c[2]),

a1(c[2], s[1], x[1], y[1], c[1]),

a0(c[1], s[0], x[0], v[0], ci);

endmodule

```

#### 問題5 (加算回路の設計)

- ・前頁による実装ではnビットの加算器は作れない。なぜなら,faモジュールをn個宣言することがverilogではできないからである。では,nビット加算器はどうすれば実装できるか?faモジュールを用いずにビットベクトルを使ってnビット加算器を作成せよ。

- ・このモジュールはadd4 のように、最上位の桁上げcu と、最下位に加えるci を持つこと。

- さらに、シミュレーションにより評価せよ。

#### (ヒント)

問題を解く肝になるのは、add4の"fa a3(~), a2(~)…a0(~);"の部分をいかにビットベクトルを用いて書き直すかである。次ページを参考に考えてみてください。

- 例: 4 bit加算器の場合

- 入力 被加数 x[3:0],加数 y[3:0],最下位の桁上げ ci

- 出力 加算結果 s[3:0],最上位の桁上げ cu

- 途中の桁上げ c[3:0]

c[3]…3桁目からの桁上げ, c[2]…2桁目からの桁上げ

c[1]…1桁目からの桁上げ, c[0]…0桁目からの桁上げ(=ci)

$$x[3] + y[3] + c[3] = \begin{bmatrix} \vdots & \vdots & \vdots \\ cu & s[3] \end{bmatrix}$$

$$x[2] + y[2] + c[2] = \begin{bmatrix} \vdots & \vdots & \vdots \\ c[3] & s[2] \end{bmatrix}$$

$$x[1] + y[1] + c[1] = \begin{bmatrix} \vdots & \vdots & \vdots \\ c[2] & s[1] \end{bmatrix}$$

$$x[0] + y[0] + c[0] = \begin{bmatrix} \vdots & \vdots & \vdots \\ c[1] & s[0] \end{bmatrix}$$

•4つの式をビットベクトルでまとめると?

$x[0] ^ y[0] ^ c[0] = s[0]$

・4桁からn桁に拡張した場合どういう式になる?

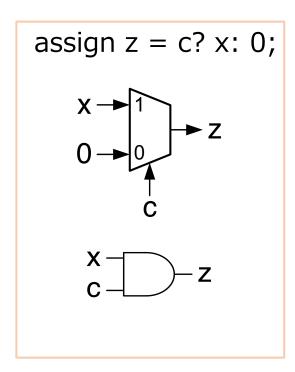

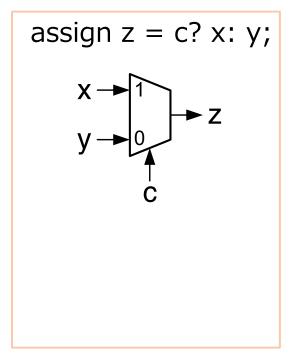

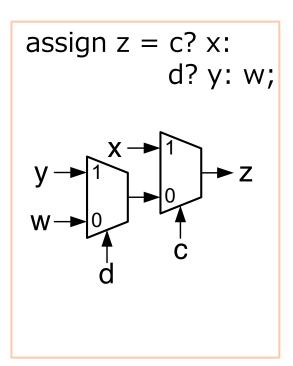

### 条件付きassign文

assign 変数= 条件? 条件が1(真) のときの値: 条件が0(偽) のときの値;

・条件はC言語と同じ >,<, >=,<=, ==, !=, <=などが, またその論理積(&&)や論理和(||)などが利用できる

#### 繰り返し動作の記述(参考程度)

for (制御変数の初期設定; 継続条件; 制御変数の変更) 文;

```

module sel( z, x, c );

parameter n = 4;

input [n-1: 0] x;

input c;

output [n-1: 0] z;

assign z = c? x: 0;

endmodule

```

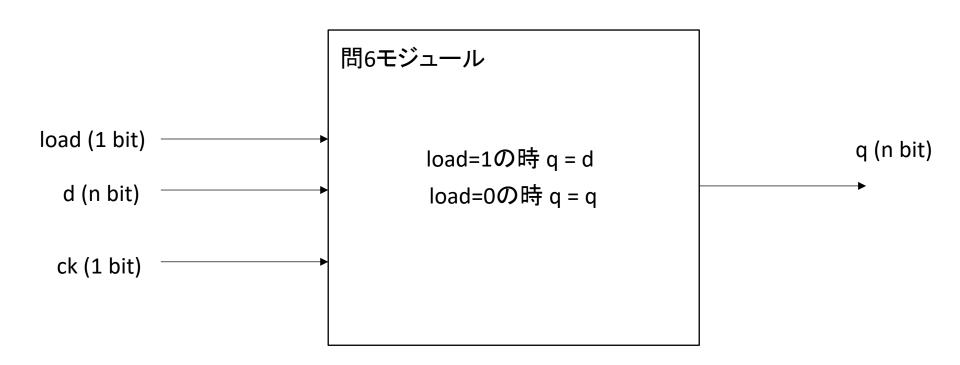

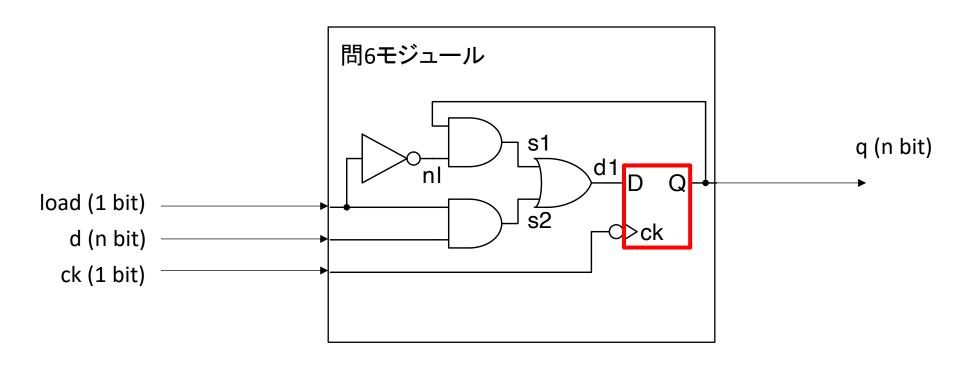

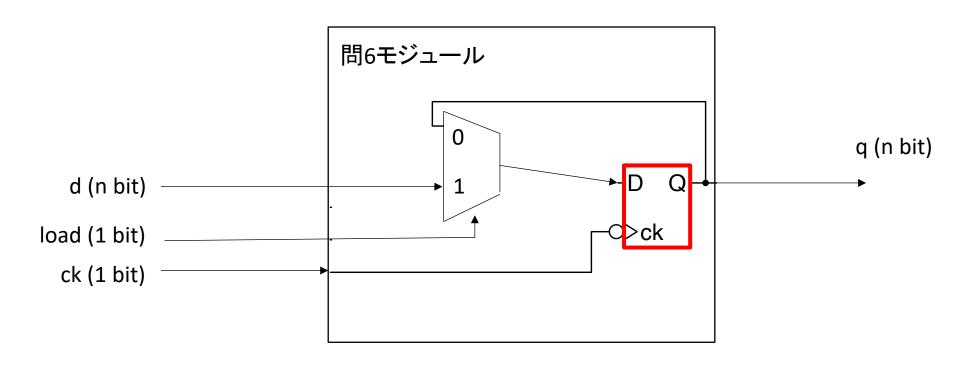

- クロック同期して動作し、以下に示す仕様を満たすnビットレジスタのモジュールrを設計し、シミュレーションにより評価せよ。

- ちなみに1ビットレジスタの例はP.49に載せている。

- ・この問題では、P.49の1ビットレジスタに対して

- ①データのビット幅をnビットに拡張

- ②セレクタを用いて回路をより簡単化 すること

- データ入力: *d, ck*

- ·制御信号入力: load

- ・データ出力: q

- ・動作: load = 0 のときq = q

- load = 1 のときq = d

load=1の時 q = d

load=0の時 q = q

#### 問題7 (加減算回路の設計)

・問題5の加算回路をベースに、以下の仕様のn桁の加減算回路のモジュールを設計し、シミュレーションにより評価せよ。ただし負の数は2の補数表現とする。

数の入力: n 桁の整数x, y

制御信号入力: k

・出力: 桁上げcu とn 桁の和s

•動作: k=0 のときs=x+y

k=1 のときs=x-y

負数を2の補数で表したとき、x-y=x+y+1である. したがって, kの値によって $y \ge y$ の何れかを選ぶ選択回路の出力とxを加算すればよく, 1の加算には、桁上げ入力を使う.

# オプション課題

### 問題8 オプション課題

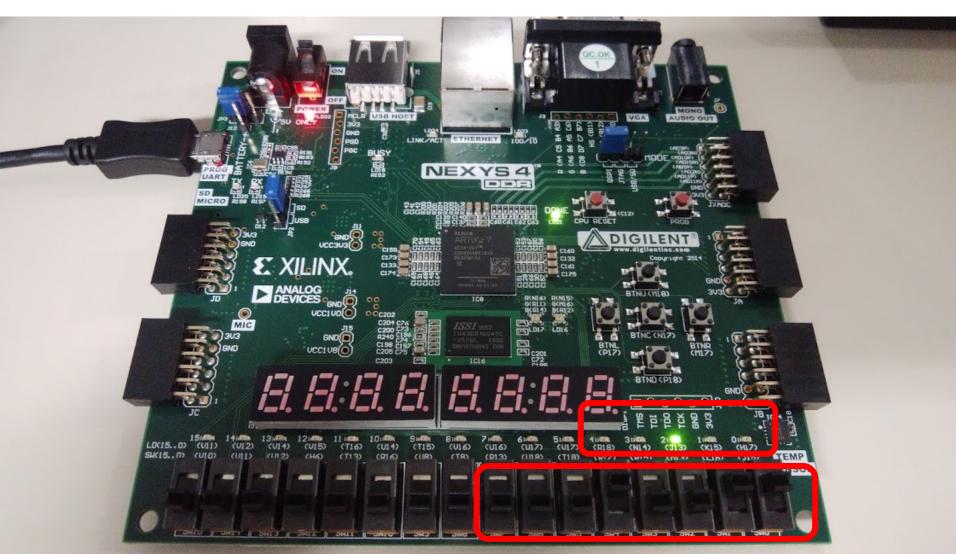

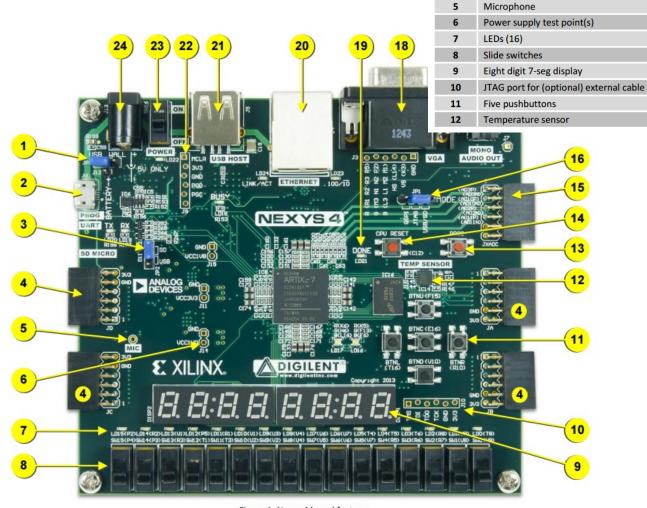

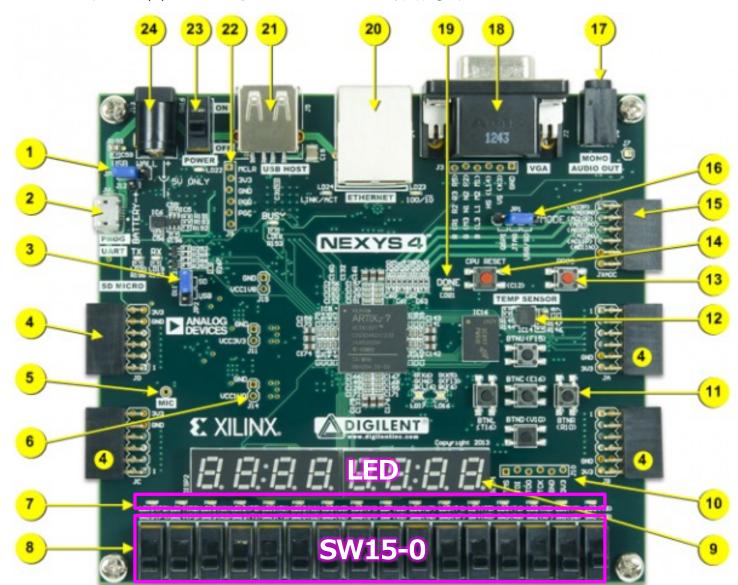

Xilinx VivadoとNEXYS 4を用いて, 加算器(問題5のadd4モジュール)を FPGA上で動作させよ.

以下のURL からファイルをダウンロードし、作成したディレクトリに保存 http://www.hpc.is.uec.ac.jp/yamaki\_lab/experiment/add4\_nexys4.xdc (コンソールでwget http://www.hpc.is.uec.ac.jp/yamaki\_lab/experiment/add4\_nexys4.xdc ~/mics\_J2/)

#### **NEXYS 4**

Figure 1. Nexys 4 board features

**Callout**

1

2

3

**Component Description**

Pmod port(s)

Shared UART/ JTAG USB port

Power select jumper and battery header

External configuration jumper (SD / USB)

**Callout**

13

14

15

16

17

18

19

20

21

22

23

24

**Component Description**

FPGA configuration reset button

CPU reset button (for soft cores)

Analog signal Pmod port (XADC)

Programming mode jumper

FPGA programming done LED

PIC24 programming port (factory use)

Audio connector

VGA connector

Ethernet connector

**USB** host connector

Power switch

Power jack

### add4の実行

・SW7-0の切り替えに応じてLEDが点灯する

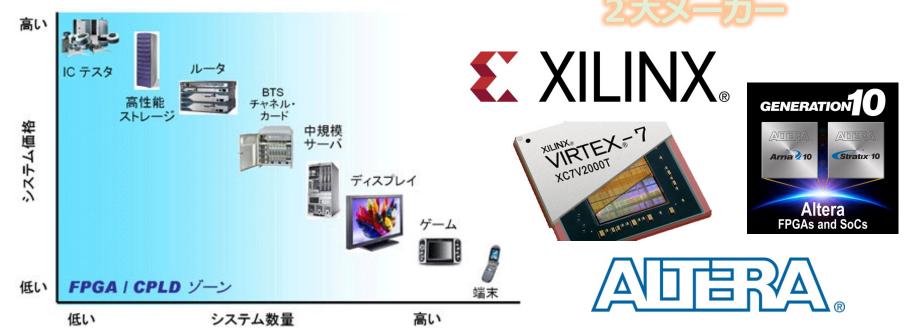

#### FPGAの用途

- FPGA

- Field Programmable Gate Array

- ・ユーザが論理機能を何度でも書き換え可能

- ・少量多品種・短ライフサイクル品

- ASIC

- Application Specific Integrated Circuit

- 回路の論理が固定の特定アプリケーション用のカスタム品

- プロセッサ等の大量生産品

# xdcファイル:FPGAのピン配置を決めるファイル まずはFPGAボードを確認

#LED vivado 計算結果を出力するLED(1だと点灯、0だと無灯)

```

set_property PACKAGE_PIN R18 [get_ports {cu}]

set_property IOSTANDARD LVCMOS33 [get_ports {cu}]

set property PACKAGE PIN N14 [get ports {s[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {s[3]}]

set_property PACKAGE_PIN J13 [get_ports {s[2]}]

set property IOSTANDARD LVCMOS33 [get_ports {s[2]}]

set_property PACKAGE_PIN K15 [get_ports {s[1]}]

set property IOSTANDARD LVCMOS33 [get_ports {s[1]}]

set_property PACKAGE_PIN H17 [get_ports {s[0]}]

set property IOSTANDARD LVCMOS33 [get_ports {s[0]}]

#PUSH BUTTON

set property PACKAGE PIN N17 [get ports {ci}]

set property IOSTANDARD LVCMOS33 [get_ports {ci}]

```

# xdcファイル:FPGAのピン配置を決めるファイル まずはFPGAボードを確認

#SWITCH vivado 4ビットの値を入力するスイッチ

```

set_property PACKAGE_PIN R13 [get_ports {x[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[3]}]

set property PACKAGE PIN U18 [get ports {x[2]}]

set property IOSTANDARD LVCMOS33 [get_ports {x[2]}]

set property PACKAGE PIN T18 [get ports {x[1]}]

set property IOSTANDARD LVCMOS33 [get_ports {x[1]}]

set property PACKAGE PIN R17 [get ports {x[0]}]

set property IOSTANDARD LVCMOS33 [get_ports {x[0]}]

set property PACKAGE PIN R15 [get ports {y[3]}]

set property IOSTANDARD LVCMOS33 [get_ports {y[3]}]

set property PACKAGE PIN M13 [get ports {y[2]}]

set property IOSTANDARD LVCMOS33 [get ports {y[2]}]

set_property PACKAGE_PIN L16 [get_ports {y[1]}]

set property IOSTANDARD LVCMOS33 [get_ports {y[1]}]

set property PACKAGE PIN J15 [get ports {y[0]}]

set property IOSTANDARD LVCMOS33 [get_ports {y[0]}]

```

### Vivadoを起動

- Terminal で vivado と入力

- Create New Projectをクリック

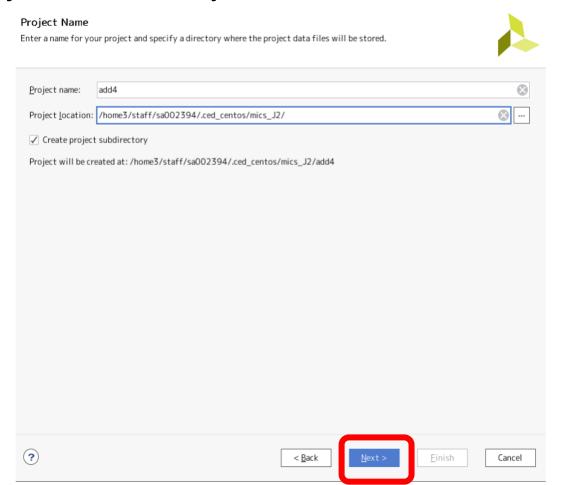

### プロジェクトディレクトリを指定

- Project name: add4

- Project location: 任意のディレクトリ

- Create project Subdirectoryにチェック

### プロジェクトタイプの指定

#### RTLプロジェクトにチェック

#### Project Type

Specify the type of project to create.

| • | <u>R</u> TL Project You will be able to add sources, create block designs in IP Integrator, generate IP, run RTL analysis, synthesis, implementation, design planning and analysis. |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Do not specify sources at this time                                                                                                                                                 |

| 0 | Post-synthesis Project: You will be able to add sources, view device resources, run design analysis, planning and implementation.                                                   |

|   | Do not specify sources at this time                                                                                                                                                 |

| 0 | _I/O Planning Project Do not specify design sources. You will be able to view part/package resources.                                                                               |

| 0 | <u>Imported Project</u> Create a Vivado project from a Synplify, XST or ISE Project File.                                                                                           |

| 0 | E⊻ample Project<br>Create a new Vivado project from a predefined template.                                                                                                          |

|   |                                                                                                                                                                                     |

|   |                                                                                                                                                                                     |

|   |                                                                                                                                                                                     |

|   |                                                                                                                                                                                     |

|   |                                                                                                                                                                                     |

|   |                                                                                                                                                                                     |

| ? | < <u>B</u> ack <u>N</u> ext > <u>E</u> inish Cancel                                                                                                                                 |

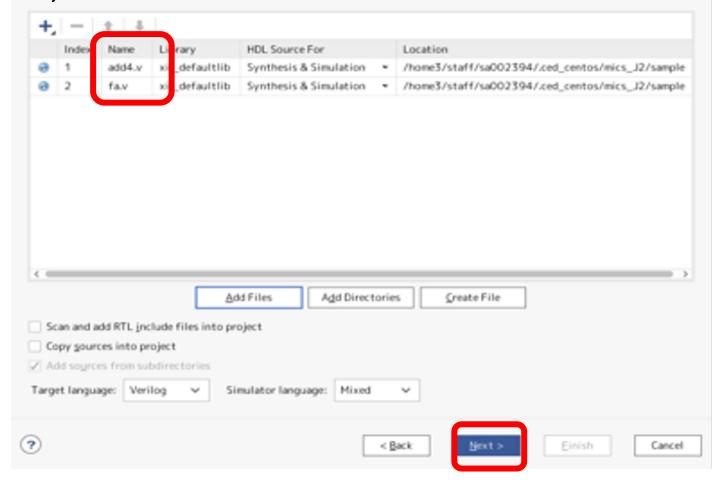

### ソースファイルの指定

② Add filesで次のファイルを追加 add4.v, fa.v

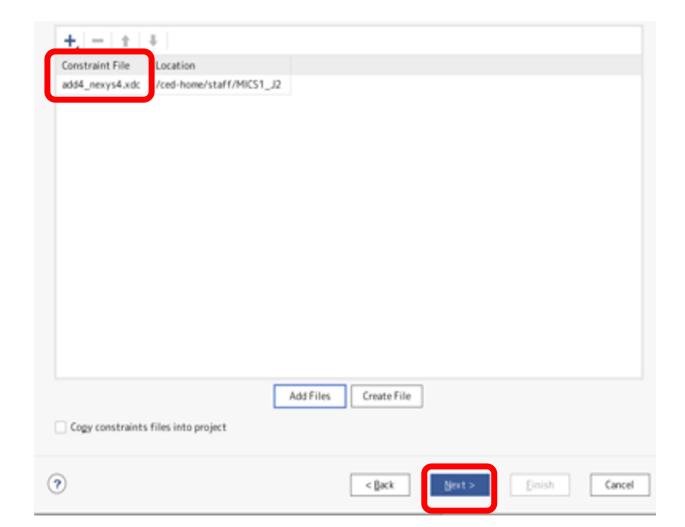

### 制約ファイルを追加

② Add filesで次のファイルを追加 add4\_nexys4.xdc

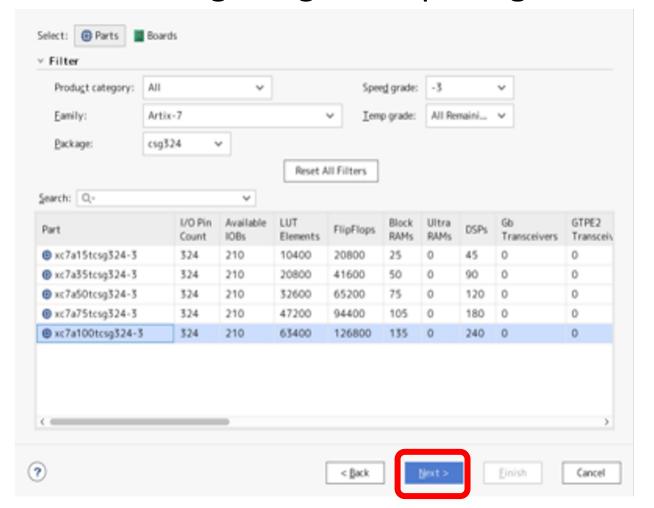

## デバイスの指定: XC7A100T-CSG324を選択

Pamily: Artix-7 Package: csg324 Pspeed grade: -3

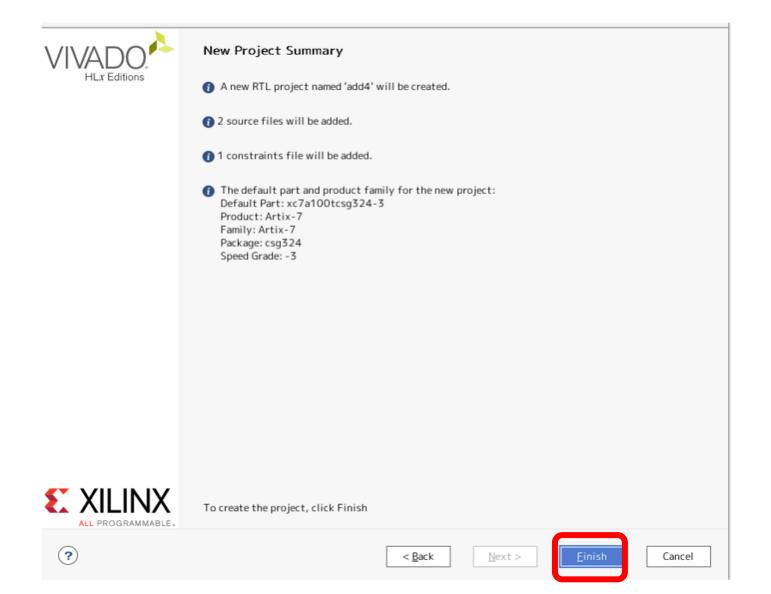

### 設定内容を確認

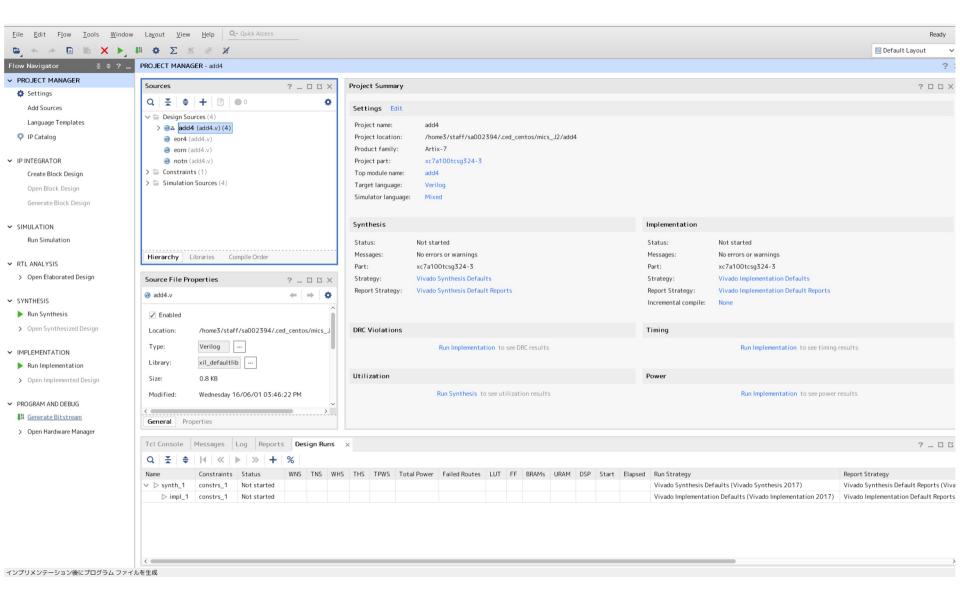

### Vivadoプロジェクトトップページ

### コンパイルの実行

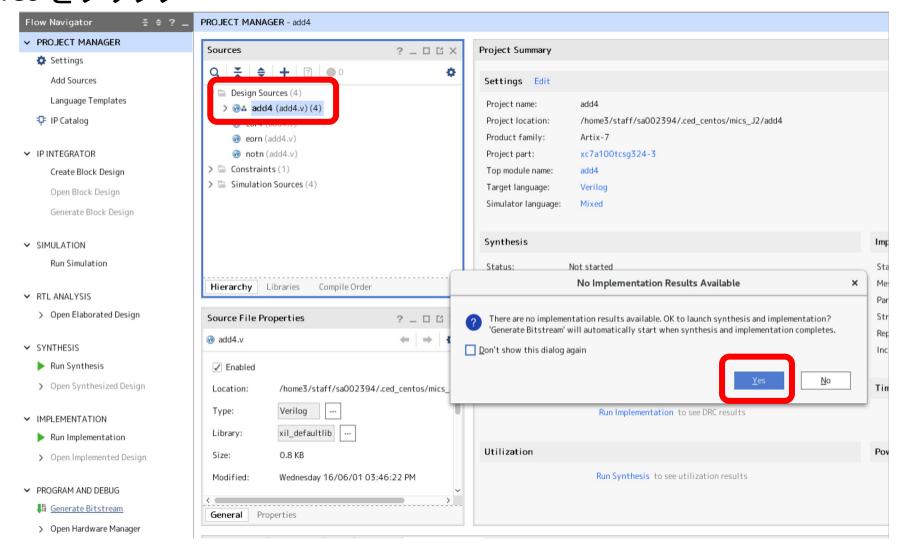

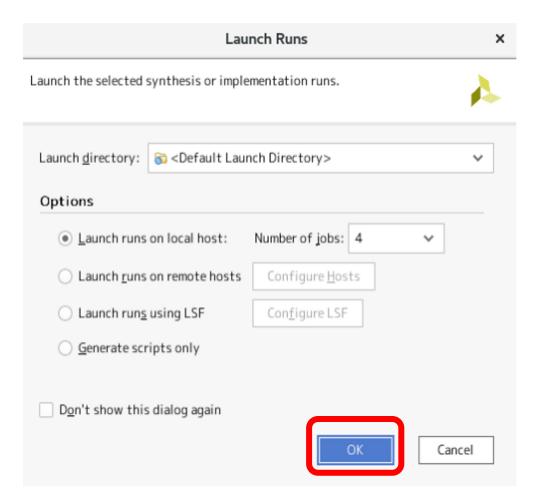

Sources ウィンドウで add4 を選んで Generate Bitstream を実行し Yes をクリック

### コンパイルの実行

#### OKをクリック

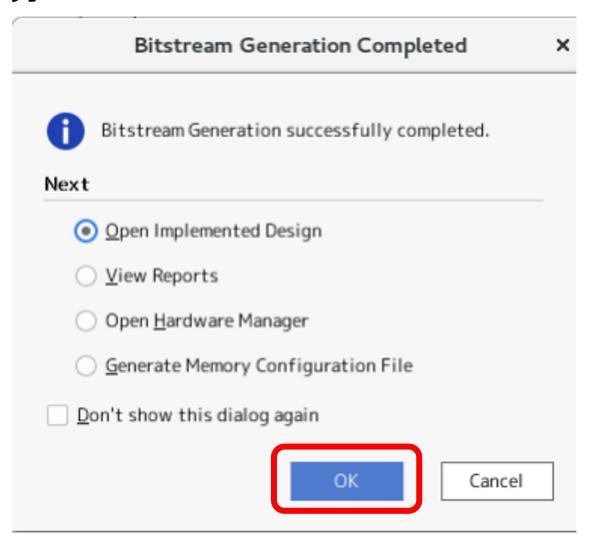

### コンパイル成功

Bitstream Generation successfully completed が でたら成功

### FPGAの電源を入れる

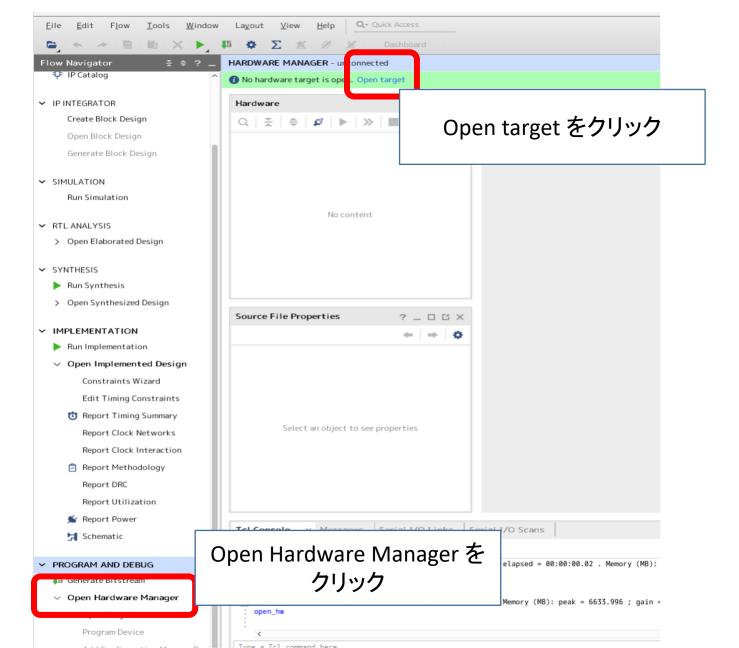

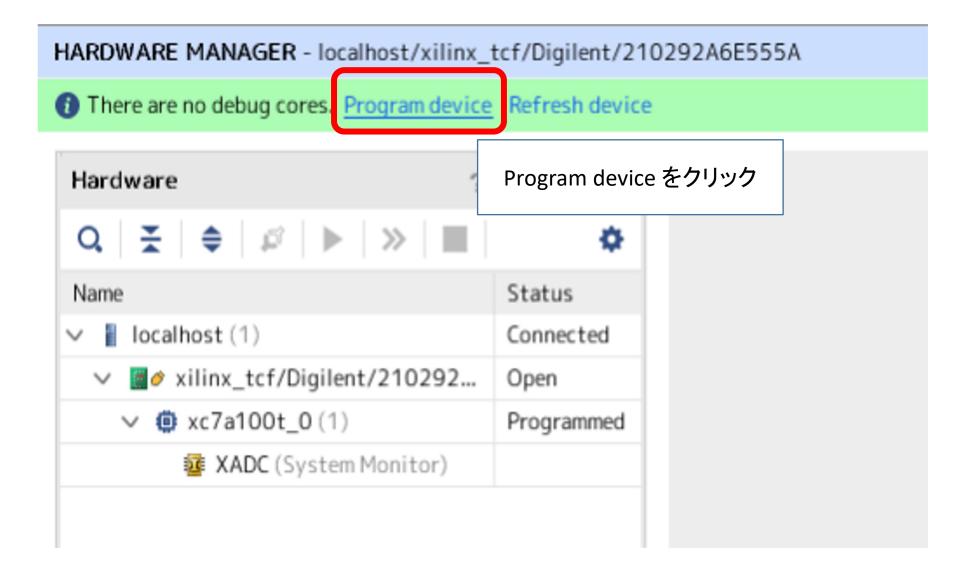

### FPGAへ書き込み

### FPGAへ書き込み

### FPGAへ書き込み

#### Program Device

×

Select a bitstream programming file and download it to your hardware device. You can optionally select a debug probes file that corresponds to the debug cores contained in the bitstream programming file.

| Bitstre <u>a</u> m file:   | :aff/sa002394/.ced_centos/mics_J2/add4/add4.runs/impl_1/add4.l |

|----------------------------|----------------------------------------------------------------|

| Debug probes file:         |                                                                |

| ✓ <u>E</u> nable end of st | artup check                                                    |

|                            | Program をクリック                                                  |

| ?                          | <u>P</u> rogram Cancel                                         |

## add4の動作確認 例:0011+0001=0100